# Higher Transition Temperature in p-Type VO<sub>2</sub>

Luke Hellwig

Carleton College, 1 North College Street, Northfield, MN 55057 and University of California, Davis, 1 Shields Ave., Davis, CA, 95616

Xingyue Peng and Dong Yu

University of California, Davis, 1 Shields Ave., Davis, CA, 95616

We report the growth of free-standing, 100-nm-thick, vanadium dioxide (VO<sub>2</sub>) nanowires on an unpolished quartz substrate. Device gating revealed that many of the nanowires were p-type, making us the first group to report p-type VO<sub>2</sub> nanowires. Temperature dependence measurements show an elevated phase transition region of 80 °C to over 125 °C. Scanning photocurrent microscopy showed the formation of small, separated metal domains in the nanowire, along with photocurrent spots due to band bending at the metal-semiconductor junction. We also discuss future research directions that could lead to better understanding of the novel behavior we report.

### I. INTRODUCTION

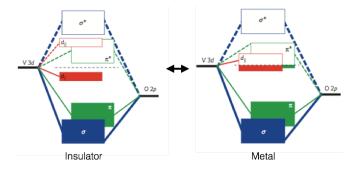

Vanadium dioxide  $(VO_2)$  is a strongly correlated electron material with a first order insulator-metal phase transition at 68 °C. Physicists have long debated the mechanism behind the phase transition in the material. Recently, the theory that  $VO_2$  undergoes a Mott transition has emerged as the most popular explanation.<sup>1</sup> When the carrier concentration in  $VO_2$  increases with increasing temperature, the carriers can trigger a structural change in the material, which in turn changes the material's energy band structure (see Fig. 1).<sup>2</sup> The shifted band structure causes electrons to partially fill two energy bands, allowing high temperature  $VO_2$  to conduct electric current. The wide range of transition-triggering conditions, such as electric fields, light, and applied strain, allow for applications of  $VO_2$  that include field effect transistors,<sup>3</sup> photonic transistors,<sup>4</sup> strain gauges,<sup>5</sup> thermal transistors,<sup>6</sup> and gas sensors.<sup>7</sup>

Previously, our group published a study of VO<sub>2</sub> nanowires grown in a lab at the University of California, Berkeley using a vapor deposition method.<sup>8</sup> With a width of 1 µm, these nanowires functioned as one dimensional systems with regards to their metallic domains, offering a unique perspective into the fundamental behavior of VO<sub>2</sub>.<sup>9</sup> Our lab found that the n-type nanowires displayed an unusually long free carrier lifetime, and also observed band being within the nanowires due to Schottky barriers.<sup>9</sup>

Our objectives for this summer were to grow similar  $VO_2$  nanowires in our lab and to compare their electronic behavior to that of the Berkeley nanowires. We were successful in growing nanowires with one tenth of the diameter of the Berkeley wires. Device gating measurements indicated that many of the wires grown were p-type, making us only the second group to report p-type  $VO_2$  and the first group to realize p-type nanowires.<sup>10</sup> A phase transition was recorded in a  $VO_2$  device at a much higher temperature than the expected transition temperature of 68 °C. Scanning photocurrent microscopy (SPCM) showed the formation of small metal domains

on the wire at 120 °C and confirmed that the nanowires were p-type.

## II. METHODS

We grew VO<sub>2</sub> nanowires using a vapor deposition method with a V<sub>2</sub>O<sub>5</sub> powder source. Deposition occurred in an evacuated tube at 3.5–4 Torr of pressure with argon flowing through the tube at 150–200 sccm. The powder was heated to 880 °C. Two separate growths were used to make nanowires for device application. In the first growth, the powder was heated for three hours with an argon flow rate of 150 sccm. The growth time for the second growth was one hour with an argon flow rate of 200 sccm. In both growths, VO<sub>2</sub> was deposited on an unpolished quartz substrate at 880 °C. The roughness of the substrate caused free-standing nanowires to grow out from the substrate surface.<sup>8</sup>

Atomic force microscopy (AFM) showed that the thickness of wires from the first growth was 100 nm. Assuming a square cross section (as is typical for  $VO_2$  nanowires),<sup>11</sup> the cross sectional area of the wires was

FIG. 1. Band structure diagram for insulating and metallic phases of VO<sub>2</sub>. At low temperatures, electron-electron interactions cause the splitting of the  $d_{\parallel}$  band, and the monoclinic structure of insulating VO<sub>2</sub> raises the anti-bonding  $\pi *$  band relative to its position in the material's tetragonal structure as a metal.<sup>2</sup>

$0.01 \text{ }\mu\text{m}^2$ , one hundredth of the cross sectional area of the VO<sub>2</sub> nanowires previously studied by our group.<sup>9</sup>

We transferred nanowires to a silicon chip with an  $SiO_2$  top layer of thickness 300 nm, pre-patterned with contacts. We used electron beam lithography to deposit contacts connecting nanowires to the pre-patterned contacts. While making devices from the second growth, we heated the nanowires to 70-80 °C and specifically selected wires that either did or did not show the formation of metal domains, which we could see under an Olympus 51X microscope with 100X objective magnification. The lithographed contact gap ranged from 10 µm to 30 µm.

A bias voltage applied across the contacts gave a linear current response, indicating ohmic contact between the lithographed contacts and nanowires. The normal resistivity of wires ranged from 1  $\Omega$ cm to 5  $\Omega$ cm, assuming uniform 0.01  $\mu$ m<sup>2</sup> cross sections.

Device gating was used to determine the doping type of the nanowires at room temperature. In general, the current I through a nanowire device is given by Ohm's Law,

$$I = \frac{V_b}{R},\tag{1}$$

where  $V_b$  is the bias voltage across the nanowire and R is the resistance of the wire. The resistance of a nanowire itself is dependent on the length,  $\ell$ , of the wire, its cross sectional area, a, and its conductivity,  $\sigma$ , following the relation,

$$R = \frac{\ell}{\sigma a}.$$

(2)

When we apply a voltage to the silicon substrate of the device chip, the system acts as a capacitor, with the SiO<sub>2</sub> top layer acting as a dielectric between the silicon gate and the nanowire. The gate voltage,  $V_g$ , linearly changes the charge concentration in the nanowire, altering the conductivity of the nanowire following the relation,

$$\sigma = n e \mu, \tag{3}$$

where n is the density of charge carriers, e is the elementary charge, and  $\mu$  is the carrier mobility in the nanowire. The change in carrier concentration depends on the sign of the applied gate voltage and the sign of the charge carriers. Combining this relation with our expressions for resistance (Eq. (2)) and current (Eq. (1)), we can see that the current through a nanowire depends on the gate voltage applied to its substrate, and that the sign of their correspondence depends on the sign of the charge carriers in the wire. Thus, by scanning the gate voltage of our devices from -100 V to 100 V, we determined their doping type and carrier concentration.

Increasing the temperature of a nanowire in the semiconductor phase increases the number of charge carriers in the conductance band. According to our expression for conductance, Eq. (3), this change in carrier density

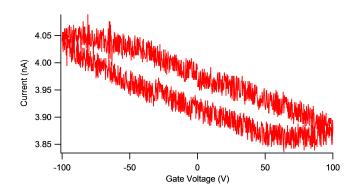

FIG. 2. Gate response for device V623 D06. A positive gate voltage creates a positive electric field through the p-type device, lowering the number of holes. The decrease in carrier concentration lowers the current through the device at a constant bias. A negative gate voltage has the opposite effect.

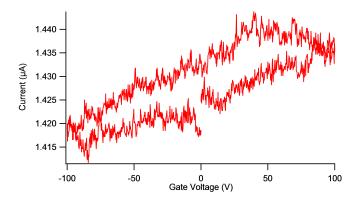

FIG. 3. Gate response for device V623 D01. The positive correlation between gate voltage and current through the device at constant bias indicates n-type doping, with positive and negative gate fields alternately creating and surpressing conduction band electrons.

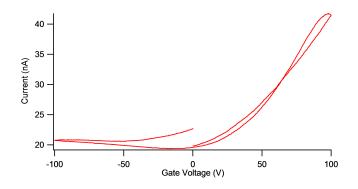

FIG. 4. Gate response for device V723 D01. The positive current-gate slope for positive gate voltages indicates the presence of electrons in this ambipolar device, whereas the negative current-gate slope for negative gate voltages means that holes also serve as charge carriers. The smaller gate response for holes indicates a higher hole concentration than electron concentration in the nanowire.

should also change the overall resistance of the wire, such that

$$I \propto \exp\left(-\frac{\Delta E}{k_B T}\right),\tag{4}$$

where I is the current through the wire at a set bias,  $\Delta E$  is the activation energy for charge carriers, T is the temperature of the wire, and  $k_B$  is the Boltzmann constant. Heating the nanowire on a purpose-built metal heating stage, we could observe the temperature dependence of the current through a nanowire at a set bias. If the relationship between temperature and current deviated from the exponential relationship (Eq. (4)), we would know that the nanowire was undergoing a phase transition.

SPCM was performed on nanowires as well, using the Olympus microscope and a continuous wave 532 nm laser beam (Compass 315M) focused on the wires.<sup>9</sup> In SPCM, the laser scanned over a 15  $\mu$ m by 15  $\mu$ m area, returning readings on the reflectivity of the area and allowing us to measure the current through the wire as a function of beam position. We were able to locate nanowires using the reflectivity readings, and then look for induced photocurrents on the wires. Total laser power on the wire was set at 10 $\mu$ W to prevent excessive heating that could trigger a local phase transition.<sup>9</sup>

### **III. EXPERIMENTS AND RESULTS**

The majority of wires tested from the first nanowire growth displayed gate responses indicative of p-type doping (see Fig. 2). Hysteresis in the gate response of the nanowires was induced by the rate of change of the gate voltage, which changed the charge on the nanowire, creating a current that depended on the sign of the change in gate voltage. The small magnitude of the gate responses revealed a high carrier concentration and low carrier mobility. Calculations based on the gate response of a typical p-type device (V623 D06) determined that the wire had a carrier concentration of  $3.1 * 10^{20}$  cm<sup>-3</sup> and a carrier mobility of 0.0051 cm<sup>2</sup>/Vs. A single wire from the first growth displayed an n-type gate response, a carrier concentration of  $9.6 * 10^{20}$  cm<sup>-3</sup>, and a carrier mobility of 0.79 cm<sup>2</sup>/Vs (see Fig. 3).

Many nanowires from the second growth displayed similarly weak p-type gate responses. However, some (less than half of those tested) displayed an unusual gate response indicative of ambipolar doping (see Fig. 4) For a typical ambipolar device (V723 D01), the n-type carrier concentration was  $5.9 * 10^{18}$  cm<sup>-3</sup> and the p-type carrier concentration was  $8.1 * 10^{19}$  cm<sup>-3</sup>.

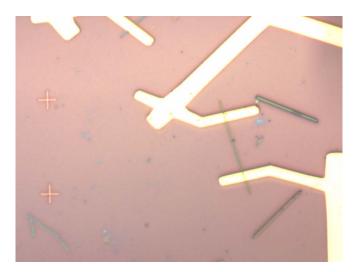

We heated a device chip from the first growth of nanowires to above the normal transition temperature of VO<sub>2</sub> at 68 °C. Optical inspection of the nine devices at this elevated temperature showed an absence of metal domains. However, several loose wires on the device chip had metallic domains (see Fig. 5). Subsequently, one of

FIG. 5. Optical image of metal domains forming on loose nanowires, taken using a 100X objective lens. Results suggest that strain induced by contacts may reduce the ability of  $VO_2$  devices to transition to metal.

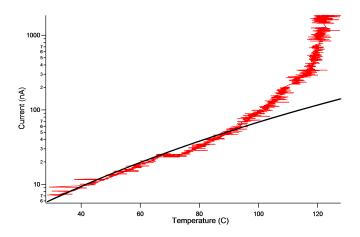

FIG. 6. Current through nanowire device V702 D03 (red) at a set bias voltage as the device was heated from room temperature to 127 °C. Black curve represents expected current curve for semiconductor phase of device based on previous heating run to 80 °C.

the nanowire devices was heated to the limit of our heating system (127 °C). The current through the nanowire at a set bias followed the expected relationship through the normal transition temperature (Eq. (4)). Above 80 °C, the relationship between current and temperature veered from the exponential relationship given in Eq. (4), indicating that the nanowire was transitioning to its metal phase (see Fig. 6). In bulk, thin films, and nanowires of VO<sub>2</sub>, the phase transition to metal is usually complete by 68 °C. Although non-semiconductor behavior began at around 80 °C, the nanowire's transition was not complete when it had reached 127 °C, indicating a much higher transition temperature.

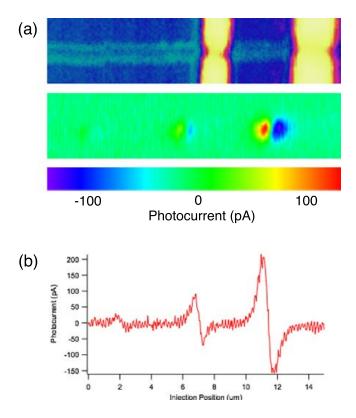

We then used SPCM at this elevated temperature to gain information about the metal domains and energy

FIG. 7. (a) SPCM reading for device V702 D03 at 120 °C. The top image shows a reflection image of the scan area. The bottom image is a map of photocurrent as a function of injection position. Negative current indicates current to the right. (b) Cross section of photocurrent map from SPCM reading.

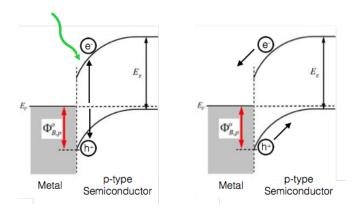

band structure of the wire (see Fig. 7). Schottky barriers at the metal-insulator interface caused photocurrent spots on either side of the metal domain (see Fig. 8). The close spacing of pairs of photocurrent spots indicated that the metal domains were small in size relative to the length of the nanowire. In addition, the direction of the photocurrent indicates p-type Schottky band bending, confirming the results of our gate scans.

### IV. DISCUSSION

Taken together, our device gating measurements and our SPCM results strongly indicate that many of the VO<sub>2</sub> nanowires grown in our lab are p-type. However, it is not clear why our growths, which were performed under similar conditions to the nanowire growths of the Berkeley group, resulted in smaller nanowires with a different doping type. There may be some subtle difference in growth methods for which we did not account. It is also possible that the Berkeley group has specifically chosen the larger nanowires from their growths for characterization, excluding small, potentially-p-type wires. More work is necessary to see if we can control the doping type and carrier concentration through growth parameters, which would help explain these differences.

More work is also needed to explain the observed elevated transition temperature of the p-type  $VO_2$ nanowires. Since the Mott phase transition relies on electron-electron interactions, it is conceivable that the lower concentration of electrons as charge carriers affects the material's transition point. However, the previous report on p-type  $VO_2$  thin films found that p-type thin films had a lower transition temperature than similar ntype films.<sup>10</sup> Another explanation for the higher transition point is strain induced by the EBL contacts. Since compressive stress can also induce a phase transition in  $VO_2$  devices,<sup>13</sup> and since the phase transition relies on a structural change in the crystal,<sup>2</sup> tensile strain applied by contacts could potentially prevent the formation of metal domains in the nanowire. This theory would explain why metal domains were seen forming on free nanowires on the first device chip at relatively low temperatures compared to the transition temperatures of the devices (Fig. 5).

Strain may also play a role in the segmented formation of metal domains as observed by SPCM and optical microscopy. Given that the nanowires are not embedded in the substrate, we would expect a single metal domain to form on the wire and then spread across the rest of the wire as the wire transitioned.<sup>14</sup> Unexpected interaction between nanowire and SiO<sub>2</sub> top layer could be responsible, as could inhomogeneities within the wire. However, no other measurement has shown evidence of excessive interaction with the substrate or inhomogeneities, so this behavior remains unexplained. Overall, further studies of nanowires grown in our lab will give us a better sense of how these multiple new behaviors interact.

FIG. 8. Band bending occurs as Schottky barriers form at metal-semiconductor junctions within  $VO_2$  nanowire. Photons absorbed at the Schottky barriers excite electron-hole pairs. Electrons and holes are driven in opposite directions due to the local electric field, generating a net current. The direction of band bending (and thus the direction of the photocurrent) depends on the semiconductor doping type.<sup>12</sup>

- <sup>1</sup> M. M. Qazilbash, M. Brehm, B.-G. Chae, P.-C. Ho, G. O. Andreev, B.-J. Kim, S. J. Yun, A. V. Balatsky, M. B. Maple, F. Keilmann, H.-T. Kim, and D. N. Basov, Science **318**, 1750 (2007).

- <sup>2</sup> N. B. Aetukuri, A. X. Gray, M. Drouard, M. Cossale, L. Gao, A. H. Read, R. Kukreja, H. Ohldag, C. A. Jenkins, E. Arenholz, K. P. Roche, H. A. Drr, M. G. Samant, and S. S. P. Parkin, Nature Physics **9**, 661 (2013).

- <sup>3</sup> M. Nakano, K. Shibuya, D. Okuyama, T. Hatano, S. Ono, M. Kawasaki, Y. Isawa, and Y. Tokura, Nature **487**, 459 (2012).

- <sup>4</sup> Z. Yang, C. Ko, and S. Ramanathan, Annual Review of Materials Research **41**, 337 (2011).

- <sup>5</sup> B. Hu, Y. Ding, W. Chen, D. Kulkarni, Y. Shen, V. V. Tsukruk, and Z. L. Wang, Advanced Materials **22**, 5134 (2010).

- <sup>6</sup> J. Zhu, K. Hippalgaonkar, S. Shen, K. Wang, Y. Abate, S. Lee, J. Wu, X. Yin, A. Majumdar, and X. Zhang, Nano Letters **14**, 4867 (2014).

- <sup>7</sup> E. Strelcov, Y. Lilach, and A. Kolmakov, Nano Letters 9,

2322 (2009).

- <sup>8</sup> C. Cheng, K. Liu, B. Xiang, J. Suh, and J. Wu, Applied Physics Letters **100**, 103111 (2012).

- <sup>9</sup> C. Miller, M. Triplett, J. Lammatao, J. Suh, D. Fu, J. Wu, and D. Yu, Physics Review B **85**, 085111 (2012).

- <sup>10</sup> C. Chen, Y. Zhao, X. Pan, V. Kuryatkov, A. Bernussi, M. Holtz, and Z. Fan, Journal of Applies Physics **110**, 023707 (2011).

- <sup>11</sup> B. S. Guiton, Q. Gu, A. L. Prieto, M. S. Gudiksen, and H. Park, Journal of the American Chemical Scoiety **127**, 496 (2005).

- <sup>12</sup> R. T. Tung, "Schottky barrier height basics," http://academic.brooklyn.cuny.edu/physics/tung/ Schottky/sbh2gap.jpg.

- <sup>13</sup> J. Cao, E. Ertekin, V. Srinivasan, W. Fan, S. Huang, H. Zheng, J. W. L. Yim, D. R. Khanal, D. F. Ogletree, J. C. Grossman, and J. Wu, Nature Nanotechnology 4, 732 (2009).

- <sup>14</sup> J. Wei, Z. Wang, W. Chen, and D. H. Cobden, Nature Nanotechnology 4, 420 (2009).